PS2接口键盘显示实验

一、 实验目的1、学习用FPGA设计简单通信协议的方法。

2、学习PS2的工作原理,扫描码的ASCII码的转换。

3、掌握VHDL编写中的一些小技巧。

二、 实验原理

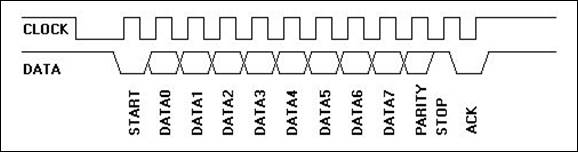

PS2通信协议是一种双向同步串行通迅协议。通迅的两端通过CLOCK(时钟信号端)同步,并通过DATA(数据端口)交换数据。任何一方如果想要抑制另外一方的通迅时,只需要把CLOCK拉到低电平。

PS2标准,规范每笔数据传输包含起始位(start bit)、扫描码(scan code)、奇同位检查(odd parity)、以及终止位(stop bit)共计11位,并以双向串行数据传输的方式,达到通信的目的。且当主机端(host)或从机端(slave)并无传送或接收数据时,数据传输端口及频率均将升为高电位。图4-17-1所示为每一笔数据传输所包含之内容如下:

1. 起始位(“0”)

2. 8位数据宽度的扫描码( scan code )。

3. 奇同位检查,使扫描码与奇同位加起来1的数字为奇数个。

4. 终止位(“1”)

图4-17-1 PS2 串行传输标准

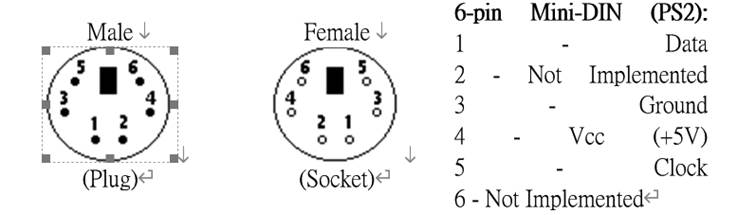

图4-17-2 PS2 端口脚位定义

PS2控制接口仅使用到两条传输端口,一为频率端口,另一则为数据端口如图4-17-2所示,且此传输埠必为三态(Tri-State)并具有双向(bidirectional)特性。PS2 传输产品上,常见为鼠标与键盘,两者的驱动原理均相同,仅扫描码(scan code)不同。因此我们以PS2键盘为例进行说明。

键盘其实就是一个大型的按键矩阵,它们由安装在电路板上的处理器(叫做“键盘编码器”)来监视着。虽然不同的键盘可能采用不同的处理器,但是它们完成的任务都是一样的,即监视哪些按键被按下,哪些按键被释放了,并将这些信息传送到主机。如果有必要,处理器处理所有的去抖动,并在它的16字节的缓冲区里缓冲数据。主机端包含了一个“键盘控制器”与键盘处理器进行通讯,并解码来自键盘处理器的信息,然后高速系统当前按键对应的处理事情。主机与键盘之间的通讯仍旧采用IBM的协议。

键盘处理器花费很多时间来扫描或监视按键矩阵。如果发现有按键按下、释放或长按,键盘就发送“扫描码”的信息到主机。扫描码有两种不同的类型:“通码”和“断码”。当一个键被按下去或长按的时候,键盘就发送通码;当一个键被释放的时候,键盘就发送断码。每个键盘被分配了唯一的通码和断码,这样主机通过查找唯一的扫描码就可以确定是哪个按键被按下或释放。每个键一整套的通断码组成了“扫描码集”,现在所有的键盘都采用第二套扫描码。由于没有一个简单的公式可以计算扫描码,所以要知道某个特定按键的通码和断码,只能采用查表的方法来获得。需要特别注意的是,按键的通码值表示键盘上的一个按键,并不表示印刷在按键上的那个字符,这就意味着通码和ASCII码之间没有任何关联。

另外,第二套通码都只有一个字节宽,但也有少数“扩展按键”的通码是两字节或四字节宽,这类码的第一个字节总是0xE0。与通码一样,每个按键在释放的时候,键盘就会发送一个断码。每个键也都有它自己的唯一的断码,不过庆幸的是,断码与断码之间存在着必然的联系。多数第二套断码有两个字长,它们的第一个字节是0xF0,第二个字节就是对应按键的通码。扩展按键的断码通常有三个字节,前两个字节0xE0和0xF0,最后一个字节是这个按键通码的最后一个字节。表4-17-1列出了键盘按键的通码和断码。

| 键值 | 通码 | 断码 | 键值 | 通码 | 断码 | 键值 | 通码 | 断码 |

| A | 1C | F0,1C | 9 | 46 | F0,46 | [ | 54 | F0,54 |

| B | 32 | F0,32 | ` | 0E | F0,0E | INSERT | 67 | F0,67 |

| C | 21 | F0,21 | - | 4E | F0,4E | HOME | 6E | F0,6E |

| D | 23 | F0,23 | = | 55 | F0,55 | PG UP | 6F | F0,6F |

| E | 24 | F0,24 | \ | 5C | F0,5C | DELETE | 64 | F0,64 |

| F | 2B | F0,2B | BKSP | 66 | F0,66 | END | 65 | F0,65 |

| G | 34 | F0,34 | SPACE | 29 | F0,29 | PG DN | 6D | F0,6D |

| H | 33 | F0,33 | TAB | 0D | F0,0D | U ARROW | 63 | F0,63 |

| I | 43 | F0,48 | CAPS | 14 | F0,14 | L ARROW | 61 | F0,61 |

| J | 3B | F0,3B | L SHFT | 12 | F0,12 | D ARROW | 60 | F0,60 |

| K | 42 | F0,42 | L CTRL | 11 | F0,11 | R ARROW | 6A | F0,6A |

| L | 4B | F0,4B | L WIN | 8B | F0,8B | NUM | 76 | F0,76 |

| M | 3A | F0,3A | L ALT | 19 | F0,19 | KP / | 4A | F0,4A |

| N | 31 | F0,31 | R SHFT | 59 | F0,59 | KP * | 7E | F0,7E |

| O | 44 | F0,44 | R CTRL | 58 | F0,58 | KP - | 4E | F0,4E |

| P | 4D | F0,4D | R WIN | 8C | F0,8C | KP + | 7C | F0,7C |

| Q | 15 | F0,15 | R ALT | 39 | F0,39 | KP EN | 79 | F0,79 |

| R | 2D | F0,2D | APPS | 8D | F0,8D | KP . | 71 | F0,71 |

| S | 1B | F0,1B | ENTER | 5A | F0,5A | KP 0 | 70 | F0,70 |

| T | 2C | F0,2C | ESC | 08 | F0,08 | KP 1 | 69 | F0,69 |

| U | 3C | F0,3C | F1 | 07 | F0,07 | KP 2 | 72 | F0,72 |

| V | 2A | F0,2A | F2 | 0F | F0,0F | KP 3 | 7A | F0,7A |

| W | 1D | F0,1D | F3 | 17 | F0,17 | KP 4 | 6B | F0,6B |

| X | 22 | F0,22 | F4 | 1F | F0,1F | KP 5 | 73 | F0,73 |

| Y | 35 | F0,35 | F5 | 27 | F0,27 | KP 6 | 74 | F0,74 |

| Z | 1A | F0,1A | F6 | 2F | F0,2F | KP 7 | 6C | F0,6C |

| 0 | 45 | F0,45 | F7 | 37 | F0,37 | KP 8 | 75 | F0,75 |

| 1 | 16 | F0,16 | F8 | 3F | F0,3F | KP 9 | 7D | F0,7D |

| 2 | 1E | F0,1E | F9 | 47 | F0,47 | ] | 5B | F0,5B |

| 3 | 26 | F0,26 | F10 | 4F | F0,4F | ; | 4C | F0,4C |

| 4 | 25 | F0,25 | F11 | 56 | F0,56 | ' | 52 | F0,52 |

| 5 | 2E | F0,2E | F12 | 5E | F0,5E | , | 41 | F0,41 |

| 6 | 36 | F0,36 |

PRNT SCRN |

57 | F0,57 | . | 49 | F0,49 |

| 7 | 3D | F0,3D | SCROLL | 5F | F0,5F | / | 4A | F0,4A |

| 8 | 3E | F0,3E | PAUSE | 62 | F0,62 |

表4-17-1PS2 键盘扫描码

三、 实验内容

本实验的任务就是利用PS2接口将键盘按键的通码在数码管上显示出来。

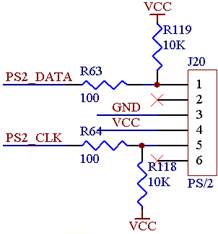

实验箱中用到PS2键盘接口与FPGA的接口电路如图4-17-3所示。

图4-17-3 PS2键盘接口电路图

四、 实验步骤

1、打开QUARTUSII软件,新建一个工程。

2、建完工程之后,再新建一个VHDL File,打开VHDL编辑器对话框。

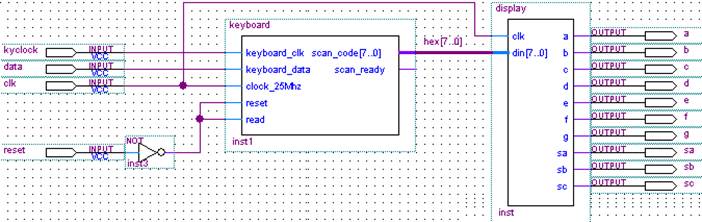

3、按照实验原理和自己的想法,在VHDL编辑窗口编写VHDL程序,用户可参照光盘中提供的示例程序。示例程序共提供2个VHDL源程序。每一个源程序完成一定的功能。其具体的功能如下表4-17-2所示:

| 文件名称 | 完成功能 |

| keyboard.VHD | PS2键盘控制器电路设计。 |

| DISPLAY.VHD | 七段显示器译码电路设计。 |

4、编写完VHDL程序后,保存起来。方法同实验一。

5、将自己编写的VHDL程序进行编译并生成模块符号文件,并对程序的错误进行修改,最终所有程序通过编译并生成模块符号文件。其具体方法请参照实验六。

6、新建一个图形编辑文件,将已生成的模块符号文件放入其中,并根据要求边接起来。完成后,如下图4-17-4所示。

图21-4 编辑好的图形设计文件

7、将自己编辑好的的程序进行编译仿真,并对程序的错误进行修改,最终通过编译。

8、编译仿真无误后,根据用户自己的要求进行管脚分配。分配完成后,再进行全编译一次,以使管脚分配生效。

9、根据实验内容用实验导线将上面管脚分配的FPGA管脚与对应的模块连接起来。

如果是调用的本书提供的VHDL代码,则实验连线如下:

CLK: FPGA时钟,接数字时钟COLCK1并将其设为24M。

DATA:PS2接口DATA信号,接PS2接口KDA端口。

KYCLOCK:PS2接口CLK信号,接PS2接口KCL端口。

RESET:复位信号,接核心板复位按键RST。

A、B、C、D、E、F、G:接七段码显示区的A、B、C、D、E、F和G

SA、SB、SC:接七段码显示区的SEL0、SEL1、SEL2。

10、用下载电缆通过JTAG口将对应的sof文件加载到FPGA中。观察实验结果是否与自己的编程思想一致。

五、 实验结果与现象

以设计的参考示例为例,将PS2接口的键盘接入PS2接口内。当设计文件加载到目标器件后,将数字信号源模块的时钟选择为24MHZ,按下PS2键盘上的键,则在实验平台的八位数码管上的中间两位将显示被按键的扫描码。观察其按下的键值所对应的扫描码是否与表4-17-1一一对应。按下核心板上的复位按键RST则停止对键盘的扫描,数码管上的扫描码不会发生改变。

六、 实验报告

1、绘出仿真波形,并作说明。

2、将实验原理、设计过程、编译仿真波形和分析结果、硬件测试结果记录下来。