数字频率计的设计

一、 实验目的1、 了解等精度测频的方法和原理。

2、 掌握如何在FPGA内部设计多种功能模块。

3、 掌握VHDL在测量模块设计方面的技巧。

二、 实验原理

所谓频率就是周期性信号在单位时间(1s)内变化的次数。若在一定时间间隔T(也称闸门时间)内测得这个周期性信号的重复变化次数为N,则其频率可表示为

f=N/T

由上面的表示式可以看到,若时间间隔T取1s,则f=N。由于闸门的起始和结束的时刻对于信号来说是随机的,将会有一个脉冲周期的量化误差。进一步分析测量准确度:设待测信号脉冲周期为Tx,频率为Fx,当测量时间为T=1s时,测量准确度为δ=Tx/T=1/Fx。由此可知这种直接测频法的测量准确度与被测信号的频率有关,当待测信号频率较高时,测量准确度也较高,反之测量准确度较低。因此,这种直接测频法只适合测量频率较高的信号,不能满足在整个测量频段内的测量精度保持不变的要求。若要得到在整个测量频段内的测量精度保持不变的要求,应该考虑待精度频率测量等其它方法。

等精度频率测频的实现方法,可以用图4-19-1所示的框图来实现。

图4-19-1 等精度测频实现框图

所谓等精度是指该频率计在所测量的整个频段内部,均可实现相同精度的测量,即测量精度与频率无关。图中预置门信号通常为1s。其内部包括一个同步门电路,用来实现被测频标与被测频率的同步,提高测量精度,减少基本误差。该部分与清零脉冲协调工作用来控制两个计数器的启动脉冲。计数器1和计数器2分别用来给频标和被测数字脉冲计数,设在同步门控制结束时计数器1计数N1,计数器2计数N2,假设频标频率为F1,被测频率位Fx,则可写出公式:

Fx/N2=F1/N1;…………………(1)

Fx=(F1/N1)* N2……………(2)

由公式可以看出,测量精度与预置门时间无关,主要由F1的频率稳定度来确定,所以为了提高测量精度,主要是提高频标的频率稳定度,换句话说,测量精度基本上近似于频标的稳定度,若频标的稳定度位10-6,则测量误差边可达到10-6。在该电路中,为了确保频标计数与被测频率完全同步(即被测频率的上升沿开始计数,1s以后,被测频率的下跳沿停止计数),同步门必须由被测信号来控制,设计方法多种多样,可由学生独立完成。

本实验采用直接测频法进行频率测量。闸门时间固定为1s,闸门信号是一个0.5Hz的方波,在闸门有效(高电平)期间,对输入的脉冲进行计数,在闸门信号的下降沿时刻,所存当前的计数值,并且清零所有的频率计数器。由于闸门时间是1s(0.5Hz方波),所以显示的频率是1s钟更新一次,且显示的内容是闸门下降沿时锁存的值。

因为闸门时间我们设定为1s,所以这种频率计仅能测出频率大于或者等于1Hz的情况,且频率越高,精度也越高。实际应用中,频率计的闸门时间是个可变量,当频率小于1Hz是,闸门时间就要适当放大。采用一个标准的时钟,在单位时间内如:0.1秒对被测信号的脉冲进行计数,即为信号的频率。

在设计频率计的时候,八个七段码管最多可以显示99,999,999Hz,因此在设计时候用八个4位二进制码(BCD码)来表示,另外还必须有同样的八个4位二进制码来对输入的频率进行计数,在闸门下降沿的时候,将后者的值锁存到寄存器中。其信号的时序关系如下图4-19-2所示:

图4-19-2 控制信号时序关系

三、 实验内容

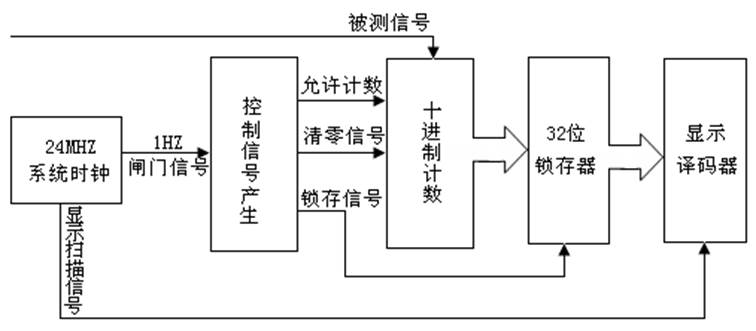

本实验要完成的任务就是设计一个频率计,系统时钟选择24MHZ的时钟,闸门时间为1s(通过对系统时钟进行分频得到),在闸门为高电平期间,对输入的频率进行计数,当闸门变低的时候,记录当前的频率值,并将频率计数器清零,频率的显示每过2秒刷新一次。其实现框图如下图4-19-3所示:

图4-19-3 测频实现框图

四、 实验步骤

1、打开QUARTUSII软件,新建一个工程。

2、建完工程之后,再新建一个VHDL File,打开VHDL编辑器对话框。

3、按照实验原理和自己的想法,在VHDL编辑窗口编写VHDL程序,用户可参照光盘中提供的示例程序。示例程序共提供6个VHDL源程序。每一个源程序完成一定的功能。其具体的功能如下表4-19-1:

| 文件名称 | 完成功能 |

| CLKOUT.VHD | 产生1HZ的闸门信号和显示扫描信号 |

| TELTCL.VHD | 在时钟的作用下生成测频的控制信号。 |

| CNT10.VHD | 十进制计数器。在实验中使用8个来进行计数 |

| SEG32B.VHD | 32位的锁存器,在锁存控制信号的作用下,将计数的值锁存 |

| DISPLAY.VHDL | 显示译码,将锁存的数据显示出来。 |

4、编写完VHDL程序后,保存起来。方法同实验一。

5、将自己编写的VHDL程序进行编译并生成模块符号文件,并对程序的错误进行修改,最终所有程序通过编译并生成模块符号文件。其具体方法请参照实验六。

6、新建一个图形编辑文件,将已生成的模块符号文件放入其中,并根据要求边接起来。

7、将自己编辑好的的程序进行编译仿真,并对程序的错误进行修改,最终通过编译。

8、编译仿真无误后,根据用户自己的要求进行管脚分配。分配完成后,再进行全编译一次,以使管脚分配生效。

9、根据实验内容用实验导线将上面管脚分配的FPGA管脚与对应的模块连接起来。

如果是调用的本书提供的VHDL代码,则实验连线如下:

CLK:FPGA时钟,接数字时钟CLOCK1,并将其设为24MHZ。

CLKIN:被测频率输入信号,可以接时钟源的其它时钟。

LEDAG[6..0]:接数码管的A、B、C、D、E、F、G。

SEL[2..0]:接数码管的SEL2、SEL1、SEL0。

10、用下载电缆通过JTAG口将对应的sof文件加载到FPGA中。观察实验结果是否与自己的编程思想一致。

五、 实验结果与现象

以设计的参考示例为例,当设计文件加载到目标器件后,从被测频率输入端口输入一个时钟信号,这时在数码管上显示这个时钟信号的频率值。。改变数字信号源的时钟,看显示的值是否与标值一致。

六、 实验报告

1、 绘出仿真波形,并作说明。

2、 根据前面介绍的等精度频率计的实现方法,写出等精度频率计的VHDL代码。

3、 将实验原理、设计过程、编译仿真波形和分析结果、硬件测试结果记录下来。