1.掌握数字基带信号的传输过程

2.熟悉位定时产生与提取位同步信号的方法

二、实验电路工作原理

数字通信系统能否有效地工作,在相当大的程度上依赖于发端和收端正确地同步。同步的不良将会导致通信质量的下降,甚至完全不能工作。通常有三种同步方式:即载波同步、位同步和群同步。在本实验中主要分析位同步。实现位同步的方法有多种,但可分为两大类型:一类是外同步法;另一类是自同步法。

所谓外同步法,就是在发端除了要发送有用的数字信息外,还要专门传送位同步信号,到了接收端得用窄带滤波器或锁相环进行滤波提取出该信号作为位同步之用。

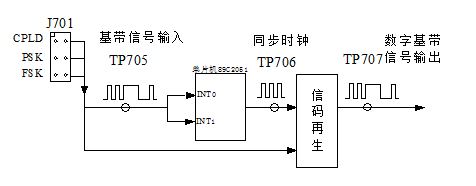

所谓自同步法,就是在发端不专门向收端发送位同步信号,而收端所需要的位元元同步信号是设法从接收信号中或从解调后的数字基带信号中提取出来。本实验中,位同步提取的就是从二相PSK信号中,对解调出的数字基带信息再直接提取恢复出位同步信号。图11-1是位同步恢复与信码再生电路方框图。

图11-1 位定时恢复与信码再生电路方框图

本实验中,我们是用单片机来实现数字基带信号的同步时钟信号的提取功能

实现思想:运用单片机的两个外部中断,实现同步时钟与外部数字基带信号同步。

具体如下:外部中断0,确定外部数字基带信号码元的长度,即所提取时钟的周期信息。当外部数字基带信号的下降沿到来时,单片机产生中断,执行计时功能,直到下一个下降沿到来,得到一个时间值。这样在一定时间范围内,只要外部数字基带信号有“101”形式存在,就可以确定所要提取时钟的周期;

外部中断1,保证所提取时钟与外部数字基带信号同步。当外部数字基带信号的上升沿到来时(或延时一定时间),单片机即开始产生并输出同步时钟。

当然了,要求提取出来的时钟很稳定,还是需要很强的实现技巧。我们这里提供的是一个16KHZ、32KHZ、64KHZ自适应的时钟提取功能软件。

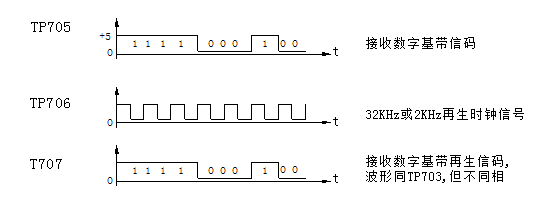

图11-2 位定时恢复电路各主要测试点波形

设计该电路时,以数字基带码元速率为32Kbit/s为例,数字基带信号由跳线开关J701输入,J701共有来自三个电路的基带信号输入,分别是:

第一排:来自CPLD可编程信号发生器产生的32Kbit/s伪随机码;

第二排:来自PSK解调电路的32Kbit/s数字基带信号;

第三排:来自FSK解调的2Kbit/s数字基带信号(未用);

上述基带信号由J701输入后,设置了一个测量点TP705,输出至位同步恢复与信码再生电路,进行位同步提取、相对码绝对码转换和信码再生功能。测量点有TP706、TP707,其中TP706是同步时钟提取测量点,TP707是相对码与绝对码转换或信码再生基带信号输出测量点。 如图11-2所示。

三、实验内容

1. 将CPLD的可编程信号发生器产生的32Kbit/s数字基带信号送入该电路中,由J701的第一排接入,观察TP705、TP706、TP707各测量点的波形;

2. 调整好PSK调制解调电路,将PSK的解调电路的32Kbit/s数字基带信号送入该电路中,由J701的第二排接入,观察TP705、TP706、TP707各测量点的波形;

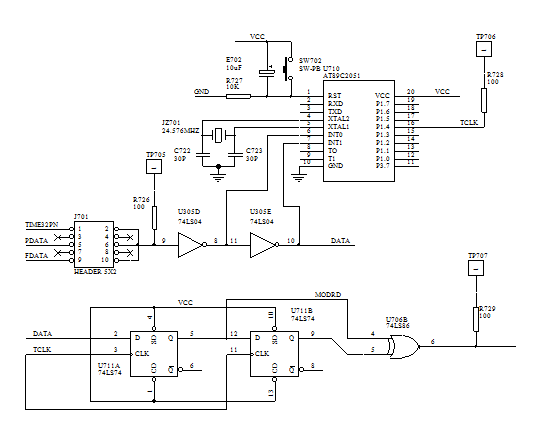

3. 调整好FSK调制解调电路,将FSK的解调电路的2Kbit/s数字基带信号送入该电路中,由J701的第三排接入,对单片机感兴趣的学生可以编程实现提取同步时钟功能,电原理图如图11-3,拧下有机玻璃罩,在断电情况下拔下单片机U710,插上仿真器即可。;

四、测量点说明

TP705:由J701输入的32Kbit/S或2Kbit/S数字基带信号,由J701选择确定。

TP706:同步时钟提取测量点波形(按复位键SW701进行复位,效果不好时,可多进行几次复位操作)。

TP707:相对码转换或信码再生基带信号输出测量点。

图11-3同步时钟提取及信码再生电原理图

五、实验报告要求

1. 画出位定时恢复与信码再生电路方框图。

2. 简述它的工作原理及工作过程。

3. 单片机编程,实现一个固定速率数字基带序列的同步时钟提取。这个比较简单,请同学试试!