2.1FPGA教学实验系统系统资源

FPGA教学实验系统是基于Altera CycloneIV器件而开发的一款数字逻辑(FPGA)创新开发平台,它可以为开发人员提供以下资源: 基于Altera CycloneIVEP4CE6E22C8N FPGA的核心板

基于Altera CycloneIVEP4CE6E22C8N FPGA的核心板 8位用户自定义按键开关

8位用户自定义按键开关 8位用户自定义拨动开关

8位用户自定义拨动开关 8位用户自定义LED灯显示

8位用户自定义LED灯显示 4X4矩阵键盘输入

4X4矩阵键盘输入 8位七段数码管显示

8位七段数码管显示 16X16矩阵点阵显示

16X16矩阵点阵显示 1602LCD字符液晶显示

1602LCD字符液晶显示 12864LCD点阵图形显示液晶屏

12864LCD点阵图形显示液晶屏 四向交通灯控制模块

四向交通灯控制模块 三层电梯模拟模块

三层电梯模拟模块 直流电机及转速测速控制模块

直流电机及转速测速控制模块 步进电机控制模块

步进电机控制模块 8位并行高速ADC转换模块

8位并行高速ADC转换模块 2路8位高速并行DAC转换模块

2路8位高速并行DAC转换模块 喇叭/蜂鸣器接口模块

喇叭/蜂鸣器接口模块 VGA控制接口模块

VGA控制接口模块 2路串行接口模块

2路串行接口模块 PS2鼠标/键盘控制模块

PS2鼠标/键盘控制模块 电源管理模块

电源管理模块2.2FPGA教学实验系统系统功能

FPGA教学实验系统是在经过长期用户需求考察后,结合目前市面上以及实际应用需要,同时兼顾入门学生以及资深开发工程师的应用需求而研发的。就资源而言,它已经涵盖了基础模块、控制类模块、通信类、单片机控制等方面的内容。

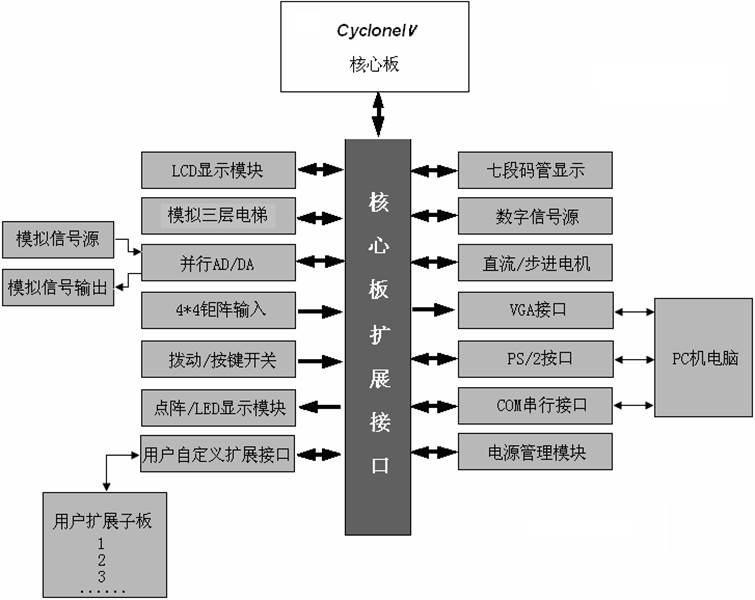

图2-1FPGA教学实验系统功能框图

本节将重点介绍开发系统所有的组成模块和各模块所在电路板的位置以及各模块在系统中所起的作用。

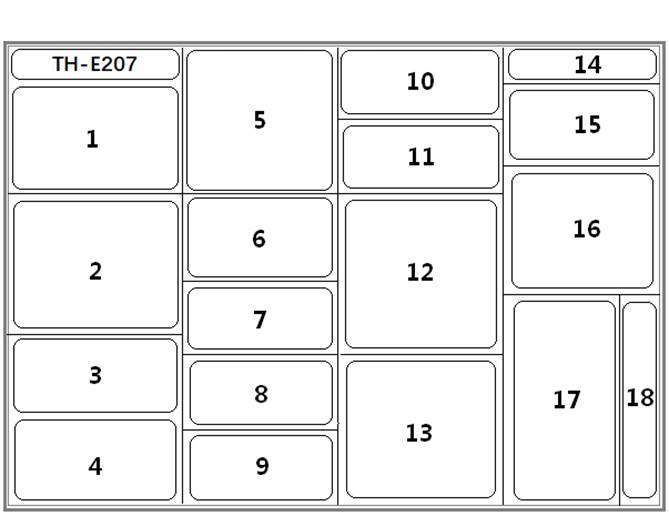

图2-2FPGA教学实验系统模块组成框图

| 模块位置 | 名称 | 功能描述 |

| 2 | Cyclone IVFPGA | 主芯片EP4CE6E22C8N核心板 |

| 输出显示模块 | ||

| 15 | 八位七段数码管 | 采用四位一体的共阴高红七段数码管两个组成八位七段数码管显示模块,用于实验中数了的显示。 |

| 7 | 八位LED灯 | 红色LED灯,用于二进制数据的显示 |

| 17 | 16X16矩形点阵 | 16X16点阵。输出简单的图形,通过连续控制可显示直观的动态效果。 |

| 1 | 12864图形点阵LCD | 提供128*64图形化点阵式液晶显示 |

| 16 | 1602字符型LCD | 用于字符显示使用 |

| 用户输入模块 | ||

| 8 | 拨动开关 | 能保持高低电平,通过手动控制为系统提供稳定的逻辑信号。 |

| 9 | 按键开关 | 不带自锁功能的按键,通过手动控制为系统提供脉冲信号。 |

| 13 | 4X4矩阵键盘 | 4×4键盘主要是通过编程实现0~F的输入,也可以作为一个控制键。 |

| 接口资源 | ||

| 16 | VGA接口 | 通过编程实现VGA显示输出 |

| 18 | PS/2接口 | 接鼠标、键盘,用于二者的控制 |

| 串行接口 | 提供2路连接PC机的串行口,用于PC机与实验系统的数据传输 | |

| 3 | 信号源接口 | 对晶振进行多级分频,能同时提供四组不同频率的方波信号供使用者选用。同时提供幅度、频度可调的模拟信号源供其它模块使用。 |

| 功能模块单元 | ||

| 5 | 直流电机 | 提供一路速度可控、可测的直流电机模块 |

| 步进电机 | 提供一路四相位步进最小7.5度步进电机 | |

| 喇叭/蜂鸣器 | 通过对其输入不同频率的信号发声 | |

| 4 | ADC转换 | 提供一个8通道8位并行ADC转换模块 |

| 10 | DAC转换 | 8位D/A转换芯片,实现D/A功能,通过程序高速连续控制可实现不同波形输出 |

| 11 | DAC转换 | 8位D/A转换芯片,实现D/A功能,通过程序高速连续控制可实现不同波形输出 |

| 6 | 交通灯 | 12个红黄绿灯交通灯方式排列,可做交通灯或舞台灯光实验 |

| 12 | 三层电梯模拟 | 模拟三层电梯的开关门、请求信号等 |

2.3 FPGA核心板模块说明

本节将重点介绍核心板所有的组成模块和各模块所在电路板的位置以及各模块在系统中所起的作用。

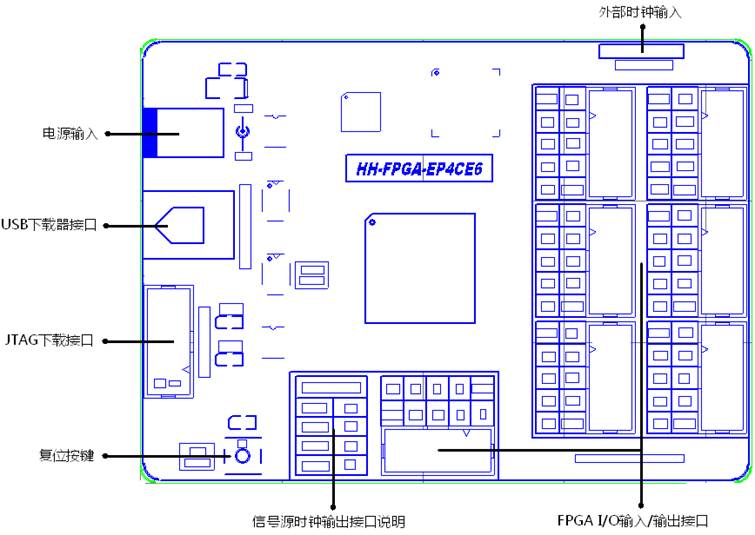

HH-FPGA-EP4CE6核心板(正面图)

图2-3核心板模块位置图

| 核心板位号 | 名称 | 功能描述 |

| U2 | CycloneIV | 主芯片EP4CE6E22C8N |

| 调试接口 | ||

| JP8 | JTAG调试接口 | JTAG供用户下载FPGA代码,下载配置芯片代码,实时调试Nios II CPU,以及运行Quartus II提供的嵌入式逻辑分析仪SignalTap II等; |

| J2 | USB调试接口 | 板载USB-BLASTER调试器功能; |

| 存储单元 | ||

| U8 | SDRAM | 8Mbytes SDRAM |

| U1 | EPCS4 | 4 Mbits主动串行配置器件 |

| 输入/输出设备 | ||

| U4 | 晶振 | 高精度50MHz时钟源,用户可以用FPGA内部PLL或分频器来得到其它频率的时钟 |

| S1 | 复位按键 | 该按键在调试Nios II CPU时,可以作为复位信号,当然也可以由用户自定义为其它功能输入 |

| 扩展接口 | ||

| JP1-JP7 | 10芯FPGA I/O输入输出插座 | 提供七个2.54mm标准间距的十芯接口供用户单独使用 |

| 电源 | ||

| J1 | 直流电源输入 | 直流电源适配器插座,适配器要求为+5V/1A |

| U3-U7 | 电源管理 | 负责提供板上所需的5V、3.3V、2.5V、1.2V电压 |

下面对板上的各个模块及其硬件连接作详细说明。

2.3.1Cyclone IV EP4CE6E22C8N

HH-FPGA-EP4CE6核心板上采用的FPGA是Altera Cyclone IV EP4CE6E22C8N,这款FPGA的资源特性如下。 6,272 LEs(逻辑单元)

6,272 LEs(逻辑单元) 270K total RAM bits

270K total RAM bits 15 Embedded multipliers(18×18硬件乘法器)

15 Embedded multipliers(18×18硬件乘法器) 2PLLs(锁相环)

2PLLs(锁相环) 91User I/O pins(用户可用I/O)

91User I/O pins(用户可用I/O) Fineline PGFP144-pin package(封装)

Fineline PGFP144-pin package(封装)2.3.2JTAG调试接口

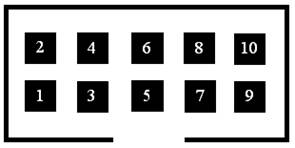

HH-FPGA-EP4CE6核心板上预留有JTAG接口供用户下载代码。JTAG接口既可以当做核心板FPGA的调试/编程接口,也可以用于对其配置器件进行编程。核心板上提供JTAG调试接口为如下图2-4所示的10针插座,其每个插针的信号定义见表2-3。

表2-3JTAG插座信号定义

注: ‘/’表示该插针没有任何信号。

2.3.3USB调试下载接口

HH-FPGA-EP4CE6核心板板载USB下载调试器,用户只需要一根USB-B连接线即可实现程序的调试和加载。2.3.4存储单元模块

FPGA配置芯片EPCS4板上使用的配置芯片为Altera公司生产的串行主动配置芯片EPCS4S08。Altera公司的串行配置器件是业界最低价格的配置器件。性能包括在系统编程(ISP)能力和多次编程能力,这种新型串行配置器件作为Cyclone™FPGA器件在大容量低价格应用领域的完美补充,使得FPGA和配置器件相结合,提供一种尽可能最低价格的完整的可编程片上系统(SOPC)解决方案。EPCS4SI8N器件的型号标识与参数如表2-4所示:

表3-3EPCS4器件参数

本核心板对其配置芯片EPCS4进行编程可以通过以下方法:

用编程电缆通过核心板上的JTAG调试接口,将QuartusII编译生成的对应配置器件的.Jic文件进行配置编程。

SDRAM存储模块

核心板的SDRAM为一片3.3V同步动态RAM容量为4M×16bits的存储空间。高速度SDRAM和高带宽数据总线,保证了Nios II CPU可以工作在非常高效的状态。

2.3.5输入/输出设备

晶振核心板上提供了高精度、高稳定性50MHz时钟,该时钟直接与FPGA的PIN-23(GCLK0)引脚相连。

如果设计人员需要其它频率时钟源,可以在FPGA内部进行分频或利用FPGA内部PLL倍频等途径来得到。

复位按键

开发板上有一个复位按键,位于核心板的左下角。复位按键上面的LED为复位指示,当复位按键按下时(低电平),LED亮。

复位按键连接到FPGA的PIN_24引脚上,可以供开发人员作为Nios II CPU的复位信号。当然也可以作为普通的按键来使用。