对于计算机组成原理课程的理解

2020-11-22 09:24 《计算机组成原理》课程是计算机科学与技术及相关专业的一门核心专业基础课,它在先导课和后续课之间起着承上启下的作用。本课程系统地介绍了单处理机系统的组成和工作原理,共有7章,第一、二章为理论基础部分,概要地介绍了计算机系统的基本组成部分,即内部存储器、中央处理器和输入输出系统,并详细地阐述了计算机中的运算方法理论;第三章详细介绍了计算机的三个核心组成部分之一,即内部存储器。指令系统是计算机软件与硬件的界面,硬件研究人员利用它实现系统功能,软件研究人员利用它编写各种系统和应用程序。第四章介绍了指令系统,然后在第五章详细地介绍了计算机系统的另外一个核心组成部分,即中央处理器的原理和指令的实现。总线是将计算机的各个组成部分互联起来的机构,第六章介绍了总线的概念、结构及工作原理。计算机通过输入输出模块与外界进行信息交换,因此,输入输出模块是计算机系统的另外一个核心组成部分,这一部分内容在第七章中介绍。 通过本课程,可以使学习者系统地掌握计算机工作的原理及各个组成部分的结构,能够分析计算机各部件的不同组织形式对系统性能的影响,从而为以后的专业学习奠定良好的理论基础。本课程适合计算机、通信及电子等相关专业的学习人员。

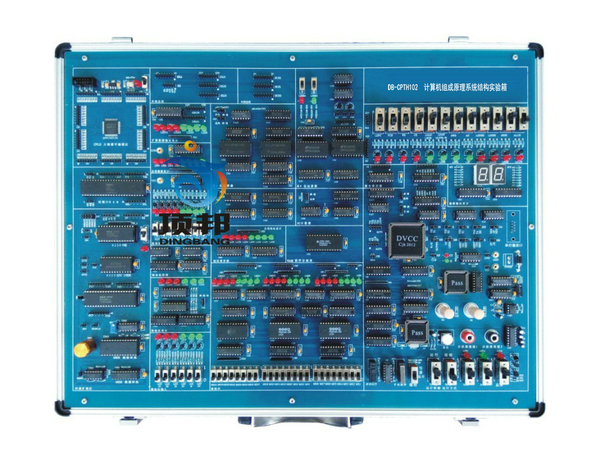

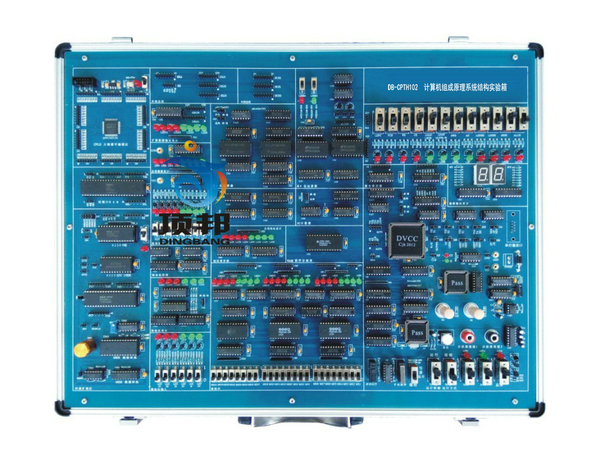

计算机组成原理系统结构实验箱由铝木合金箱体、高性能稳压电源、系统控制部件、开放式实验电路区等组成。全部实验用信号线的连接采用排线,操作方便,接触可靠。基础实验基于中小规模集成电路,综合性实验基于在系统可编程核心器件,资源完全向学开放,可以完成“计算机组成原理”、“计算机结构与逻辑设计”、“在系统编程”、“VHDL设计”、“电子系统综合设计”等课程的实验,并可以进行“专用集成电路设计”的验证实验。本实验箱适用于本专科院校计算机专业和其它相关专业的相关课程的实验和创新设计。

二、技术性能

二、技术性能

1、硬件系统采用高性能单片机89S52和LATTICE公司CPLD器件的有机结合,使系统的硬件控制电路精简而可靠。

2、提供手动、自动和联机三种工作方式,满足不同层次实验的监视需要。

3、具有完善的系统检测电路和系统保护电路设计,使实验系统更易于维护和使用。

4、系统自备双通道逻辑示波器,便于实验过程中时序信号的测量。

5、系统和电脑采用RS232/USB通信方式。

6、实验系统采用总线结构,使实验计算机具有结构简单清晰、扩展方便、灵活易变等诸多优点,实验时只要少些接线即可。

7、扩展FPGA实验模块,实现复杂模型机的设计实验。

8、专为本机配备的动态集成调试运行软件以图形化的界面显示模型机内部数据的流向和各种控制信号的状态以及时序关系。

三、硬件技术指标

1、实验电路工作电源:+5V/2A、±12V/0.5A,每路均带有短路保护和自动关断功能,每路带电源指示。其中+5V电源设计有过压、过流、欠压保护功能,待电路中故障排除后,自动恢复供电,确保设备和人身安全。

2、实验系统的字长为8位。

3、实验系统的基本指令系统类PC 机,有多种指令格式,多种寻址方式。

4、主存储器采用8K字节静态存储器6264,用于存放用户程序和数据。

5、配运算器模块,由4片4位的算术逻辑单元功能发生器级联而成。每片内实现16种二进制算术运算及16种逻辑运算,可进行8位、16位运算器实验。

6、控制器采用微程序方案实现,控存字长为24位,可用最大容量为1024字节,且用电可擦写的E2ROM存储器芯片组成,支持动态微程序设计。

7、实验系统工作频率源由555时基电路和74LS123可再触发单稳态多谐振荡器组成产生,频率范围为330HZ~580HZ。可以同时产生四种不同时序的时钟信号。

8、实验系统配有微程序手动输入并显示模块,装有24个微程序输入开关,用于输入微程序。

9、配有手动16位数据输入模块,装有16个数据输入开关,用于输入16位数据。

10、配8个控制开关,2个微动开关,用于手动控制整机的运行和切换运行方式等。

11、配2位七段数码管以显示程序运行的结果。另配置6个数码管,用于交通灯显示。

12、配微地址发生器模块和微地址显示模块、微地址控制模块。

13、配数据总线显示模块,用于显示数据总线上的动态数据。

14、配总线地址显示模块,用于显示地址总线上的动态地址。

15、配有一个双向通用移位寄存器,以实现逻辑移位功能。

16、具有超前进位控制逻辑。

17、配有指令寄存器和地址寄存器。

18、主机上设计有二片大规模 CPLD 和超强51单片机作为整机的主控器件,可以在完全自动方式下完成全部部件实验和整机模型机设计实验。

19、配有并行I/O接口电路8255,实现带输入输出接口的模型机的设计。

20、配有定时/计数器接口电路8253。实现带定时/计数器功能的模型机的设计。

21、配有中断控制器8259。实现带中断功能的模型机的设计)。

22、配有双端口存储器IDT713200。

23、模数A/D和数模D/A转换电路,实现数模和模数的转换(C9JH有)。

24、扩展ALTERA EPM240核心模块,实现具备多功能复杂模型机的设计实验。

25、实验的连接:模块间实验线路的连接:全部信号采用排线连接,操作简便,实验导线连接稳定可靠。

26、机箱:坚固型铝合金框架,厚实的 ABS 塑料包角,参考外形尺寸 480×360×150mm。

四、软件技术指标

1、实验系统集成动态调试运行软件。

2、详尽的CAI课件,能将实验原理、实验目的、芯片、查询等功能集于一体,便于多媒体教学;

3、极强的程序和微程序调试功能,有单步、断点和连续等运行方式。

4、有程序和微程序读写功能。

5、以彩色流程图方式全程监视程序的运行状态和运行结果。

6、 用debug读写存贮菜单,对寄存器进行输入数据和参数设置以及读出目标输出信息。

五、实验项目(全部提供源程序)

1、基础实验

1)8位算术逻辑运算实验

2)带进位控制8位算术逻辑运算实验

3)16位算术逻辑运算实验

4)移位运算器实验

5)存储器实验

6)微控制器实验

2、设计性使用

1)总线控制实验

2)硬布线控制器实验

3)乘法器设计实验

4)FIFO先进先出存储器实验

5)数据通路实验

6)基本模型机的设计与实现

7)扩展8255并行口实验

8)扩展8253定时/计数器实验

9)扩展8259中断控制器实验

10)扩展0809 AD转换实验

11)扩展0832 DA转换实验

12)扩展双端口存储器IDT713200实验

3、综合设计应用实验

1)带移位运算的模型机的设计与实现

2)复杂模型机的设计与实现

3)可重构原理计算机组成设计实验

4)基于CISC和RISC处理器构成的实验计算机的设计与实现

5)用大规模芯片在模型机的基础上设计一个8位输入输出并行接口芯片8212。

6)基于流水技术构成模型计算机的实验

六、实验箱配置表

DB-CPTH102 计算机组成原理系统结构实验箱

计算机组成原理系统结构实验箱由铝木合金箱体、高性能稳压电源、系统控制部件、开放式实验电路区等组成。全部实验用信号线的连接采用排线,操作方便,接触可靠。基础实验基于中小规模集成电路,综合性实验基于在系统可编程核心器件,资源完全向学开放,可以完成“计算机组成原理”、“计算机结构与逻辑设计”、“在系统编程”、“VHDL设计”、“电子系统综合设计”等课程的实验,并可以进行“专用集成电路设计”的验证实验。本实验箱适用于本专科院校计算机专业和其它相关专业的相关课程的实验和创新设计。

1、硬件系统采用高性能单片机89S52和LATTICE公司CPLD器件的有机结合,使系统的硬件控制电路精简而可靠。

2、提供手动、自动和联机三种工作方式,满足不同层次实验的监视需要。

3、具有完善的系统检测电路和系统保护电路设计,使实验系统更易于维护和使用。

4、系统自备双通道逻辑示波器,便于实验过程中时序信号的测量。

5、系统和电脑采用RS232/USB通信方式。

6、实验系统采用总线结构,使实验计算机具有结构简单清晰、扩展方便、灵活易变等诸多优点,实验时只要少些接线即可。

7、扩展FPGA实验模块,实现复杂模型机的设计实验。

8、专为本机配备的动态集成调试运行软件以图形化的界面显示模型机内部数据的流向和各种控制信号的状态以及时序关系。

三、硬件技术指标

1、实验电路工作电源:+5V/2A、±12V/0.5A,每路均带有短路保护和自动关断功能,每路带电源指示。其中+5V电源设计有过压、过流、欠压保护功能,待电路中故障排除后,自动恢复供电,确保设备和人身安全。

2、实验系统的字长为8位。

3、实验系统的基本指令系统类PC 机,有多种指令格式,多种寻址方式。

4、主存储器采用8K字节静态存储器6264,用于存放用户程序和数据。

5、配运算器模块,由4片4位的算术逻辑单元功能发生器级联而成。每片内实现16种二进制算术运算及16种逻辑运算,可进行8位、16位运算器实验。

6、控制器采用微程序方案实现,控存字长为24位,可用最大容量为1024字节,且用电可擦写的E2ROM存储器芯片组成,支持动态微程序设计。

7、实验系统工作频率源由555时基电路和74LS123可再触发单稳态多谐振荡器组成产生,频率范围为330HZ~580HZ。可以同时产生四种不同时序的时钟信号。

8、实验系统配有微程序手动输入并显示模块,装有24个微程序输入开关,用于输入微程序。

9、配有手动16位数据输入模块,装有16个数据输入开关,用于输入16位数据。

10、配8个控制开关,2个微动开关,用于手动控制整机的运行和切换运行方式等。

11、配2位七段数码管以显示程序运行的结果。另配置6个数码管,用于交通灯显示。

12、配微地址发生器模块和微地址显示模块、微地址控制模块。

13、配数据总线显示模块,用于显示数据总线上的动态数据。

14、配总线地址显示模块,用于显示地址总线上的动态地址。

15、配有一个双向通用移位寄存器,以实现逻辑移位功能。

16、具有超前进位控制逻辑。

17、配有指令寄存器和地址寄存器。

18、主机上设计有二片大规模 CPLD 和超强51单片机作为整机的主控器件,可以在完全自动方式下完成全部部件实验和整机模型机设计实验。

19、配有并行I/O接口电路8255,实现带输入输出接口的模型机的设计。

20、配有定时/计数器接口电路8253。实现带定时/计数器功能的模型机的设计。

21、配有中断控制器8259。实现带中断功能的模型机的设计)。

22、配有双端口存储器IDT713200。

23、模数A/D和数模D/A转换电路,实现数模和模数的转换(C9JH有)。

24、扩展ALTERA EPM240核心模块,实现具备多功能复杂模型机的设计实验。

25、实验的连接:模块间实验线路的连接:全部信号采用排线连接,操作简便,实验导线连接稳定可靠。

26、机箱:坚固型铝合金框架,厚实的 ABS 塑料包角,参考外形尺寸 480×360×150mm。

四、软件技术指标

1、实验系统集成动态调试运行软件。

2、详尽的CAI课件,能将实验原理、实验目的、芯片、查询等功能集于一体,便于多媒体教学;

3、极强的程序和微程序调试功能,有单步、断点和连续等运行方式。

4、有程序和微程序读写功能。

5、以彩色流程图方式全程监视程序的运行状态和运行结果。

6、 用debug读写存贮菜单,对寄存器进行输入数据和参数设置以及读出目标输出信息。

五、实验项目(全部提供源程序)

1、基础实验

1)8位算术逻辑运算实验

2)带进位控制8位算术逻辑运算实验

3)16位算术逻辑运算实验

4)移位运算器实验

5)存储器实验

6)微控制器实验

2、设计性使用

1)总线控制实验

2)硬布线控制器实验

3)乘法器设计实验

4)FIFO先进先出存储器实验

5)数据通路实验

6)基本模型机的设计与实现

7)扩展8255并行口实验

8)扩展8253定时/计数器实验

9)扩展8259中断控制器实验

10)扩展0809 AD转换实验

11)扩展0832 DA转换实验

12)扩展双端口存储器IDT713200实验

3、综合设计应用实验

1)带移位运算的模型机的设计与实现

2)复杂模型机的设计与实现

3)可重构原理计算机组成设计实验

4)基于CISC和RISC处理器构成的实验计算机的设计与实现

5)用大规模芯片在模型机的基础上设计一个8位输入输出并行接口芯片8212。

6)基于流水技术构成模型计算机的实验

六、实验箱配置表

| 序号 | 名称 | 说明 | 数量 |

| 1 | 实验主机箱 | 含详细技术指标里全部软硬件 | 1台 |

| 2 | 杜邦8芯排线 | 40cm | 5根 |

| 3 | 杜邦5芯排线 | 40cm | 2根 |

| 4 | 杜邦4芯排线 | 40cm | 2根 |

| 5 | 交流电源线1根 | 长1.5米 | 1根 |

| 6 | 软件光盘 | 联机调试软件和实验例程 | 1套 |

| 7 | 实验指导书 | 1套 |